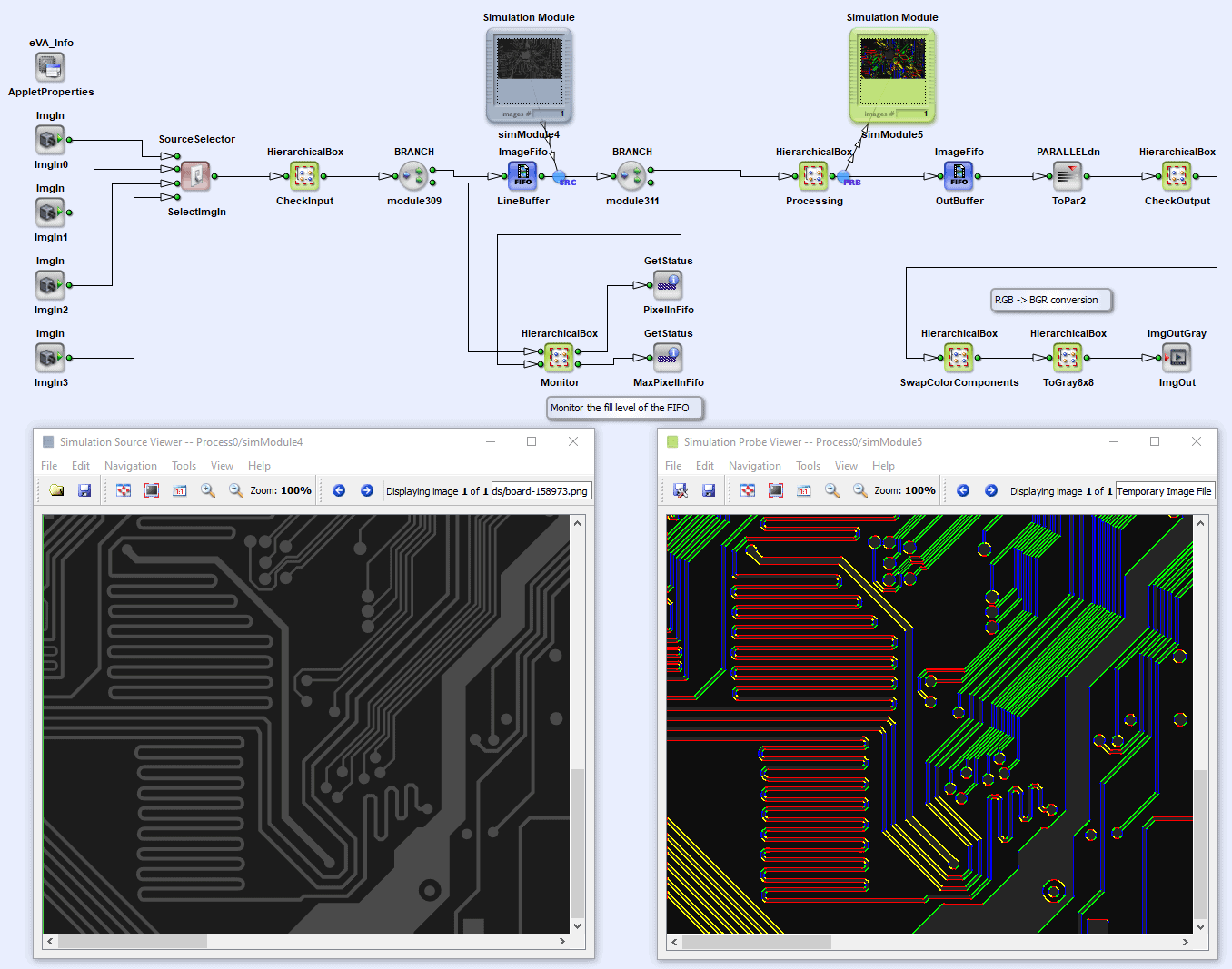

Visual Applets by Basler is a FPGA programming and design tool for creating image processing applications in a graphical manner. This makes it easy for software developers or application engineers to create complex image processing sequences within a few minutes. Programming is done graphically by a flow chart which consists of operators that are picked out of a comprehensive image processing library. It is also possible to verify the image processing system during development using simulation blocks that can be used for image generation and output visualization. This technique of visual debugging significantly decreases the development time as it is not necessary to do a compilation of the FPGA design. The hardware infrastructure is abstracted and hidden by a platform plugin. Thus, any knowledge about Hardware Description Language (HDL) or details about the FPGA itself is not required, allowing the user to focus on the image processing design.

Visual Applets – Implementation on N.A.T. hardware

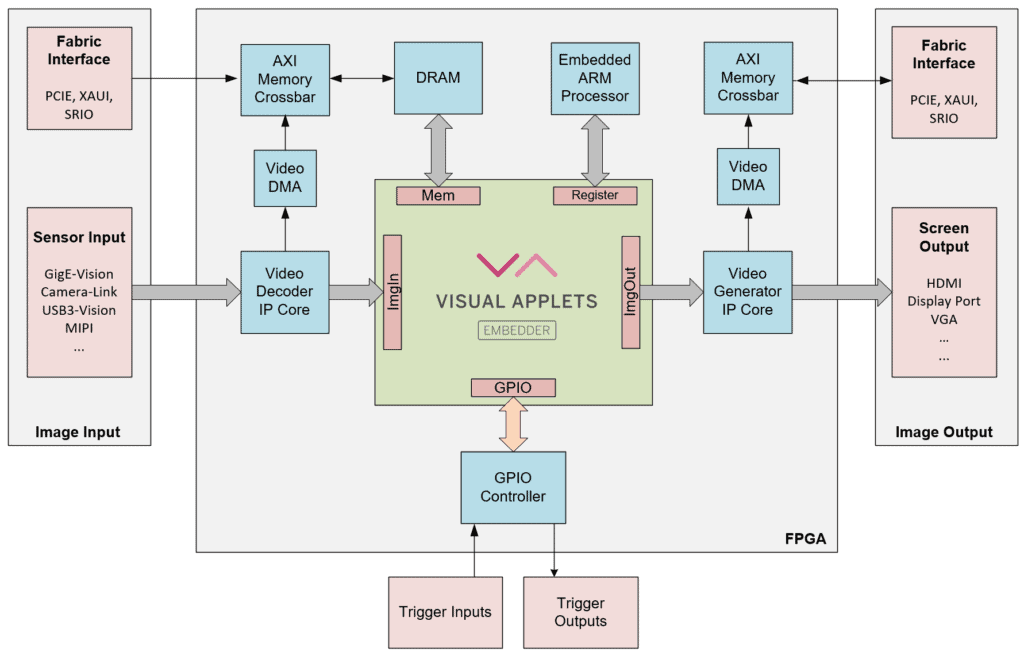

Visual Applets is embedded into NATvision hardware platforms. The eVA processing core (embedded Visual Applets) is implemented as a black-box and part of a pre-synthesized design which is provided with frame-grabber boards. The figure below shows an example implemetation of a video processing FPGA design. This design can be imported into the Visual Applets program using the platform installer .